SRGATE - Set Reset Gate

An SRGATE block produces either a high (SET) or low (RST) output. It has configurable inputs and an option to force its output independently. Both Set and Rst inputs can be selected from bit bus, and the active-edge of its inputs is configurable. An enable signal allows the block to ignore its inputs.

Fields

Name |

Type |

Description |

|---|---|---|

ENABLE |

bit_mux |

Whether to listen to SET/RST events |

SET |

bit_mux |

A falling/rising edge sets the output to 1 |

RST |

bit_mux |

a falling/rising edge resets the output to 0 |

WHEN_DISABLED |

param enum |

What to do with the output when Enable is low

0 Set output low

1 Set output high

2 Keep current output

|

SET_EDGE |

param enum |

Output set edge

0 Rising

1 Falling

2 Either

|

RST_EDGE |

param enum |

Output reset edge

0 Rising

1 Falling

2 Either

|

FORCE_SET |

write action |

Set output to 1 |

FORCE_RST |

write action |

Reset output to 0 |

OUT |

bit_out |

output value |

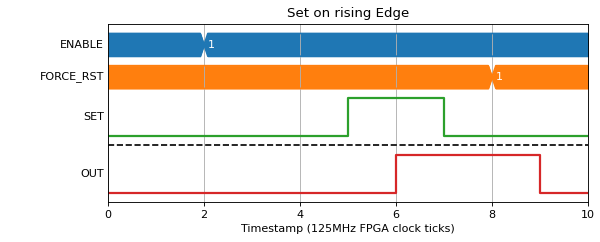

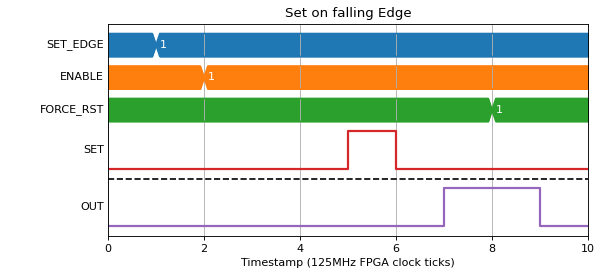

Normal conditions

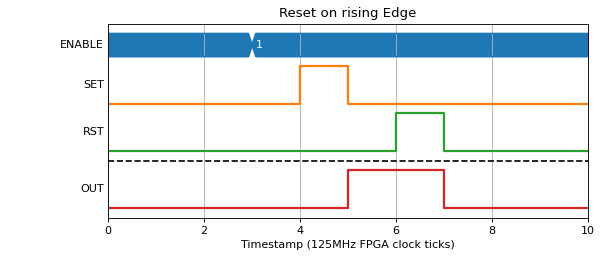

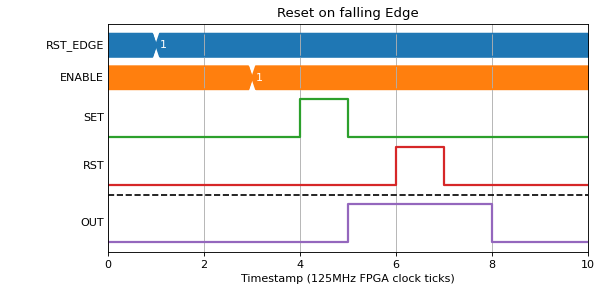

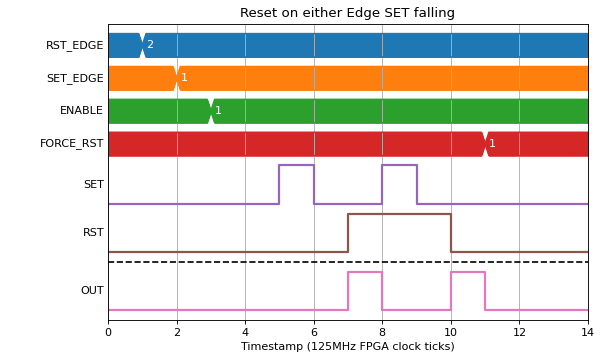

The normal behaviour is to set the output OUT on the configured edge of the SET or RESET input.

(Source code, png, hires.png, pdf)

(Source code, png, hires.png, pdf)

(Source code, png, hires.png, pdf)

(Source code, png, hires.png, pdf)

(Source code, png, hires.png, pdf)

(Source code, png, hires.png, pdf)

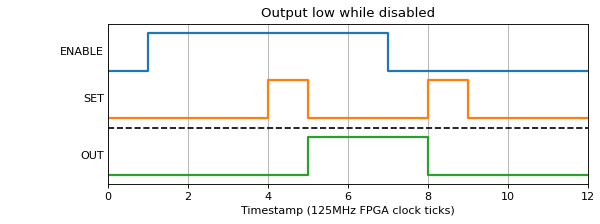

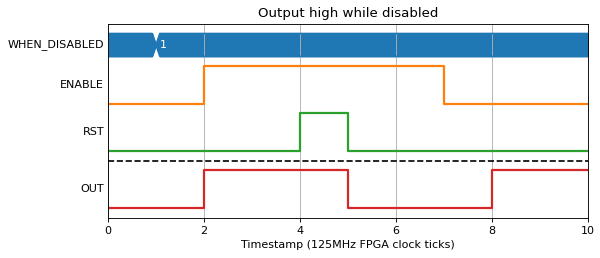

Disabling the block

The default behaviour is to force the block output low when disabled, ignoring any SET/RST events:

(Source code, png, hires.png, pdf)

The disabled value can also be set high:

(Source code, png, hires.png, pdf)

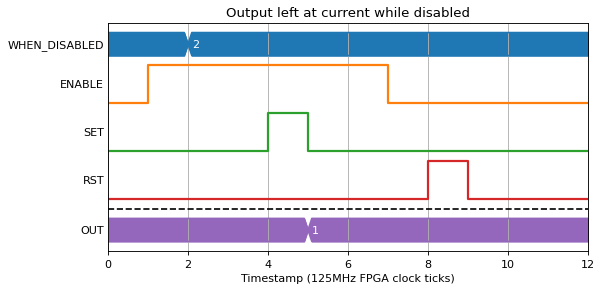

Or left at its current value:

(Source code, png, hires.png, pdf)

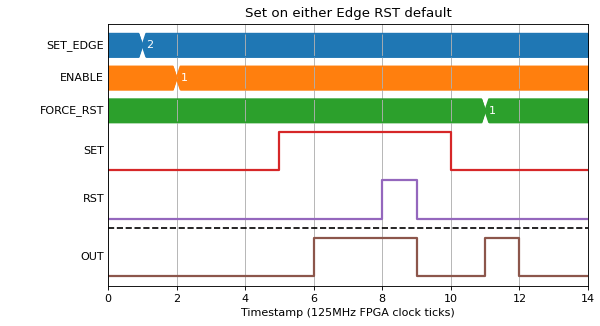

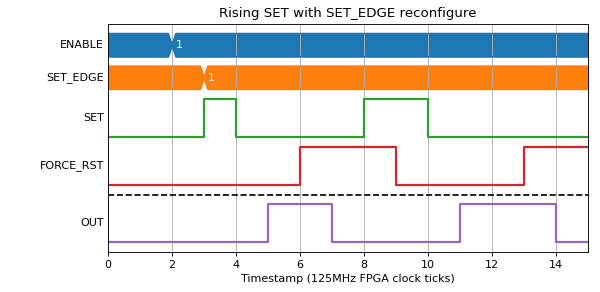

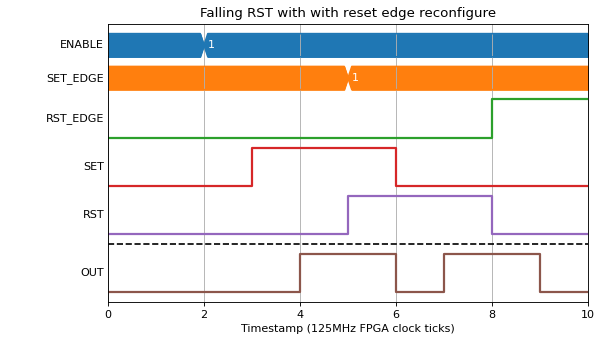

Active edge configure conditions

if the active edge is ‘rising’ then reset to ‘falling’ at the same time as a rising edge on the SET input, the block will ignore the rising edge and set the output OUT on the falling edge of the SET input.

(Source code, png, hires.png, pdf)

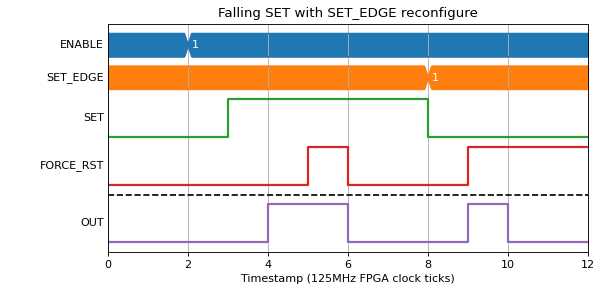

If the active edge changes to ‘falling’ at the same time as a falling edge on the SET input, the output OUT will be set following this.

(Source code, png, hires.png, pdf)

(Source code, png, hires.png, pdf)

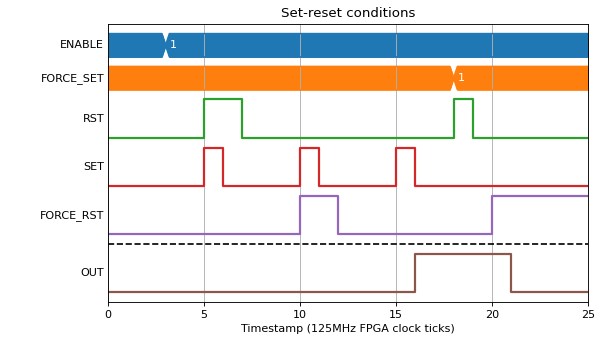

Set-reset conditions

When determining the output if two values are set simultaneously, FORCE_SET and FORCE_RESET registers take priority over the input bus, and reset takes priority over set.

(Source code, png, hires.png, pdf)